ຂໍ້ມູນຈໍາເພາະ

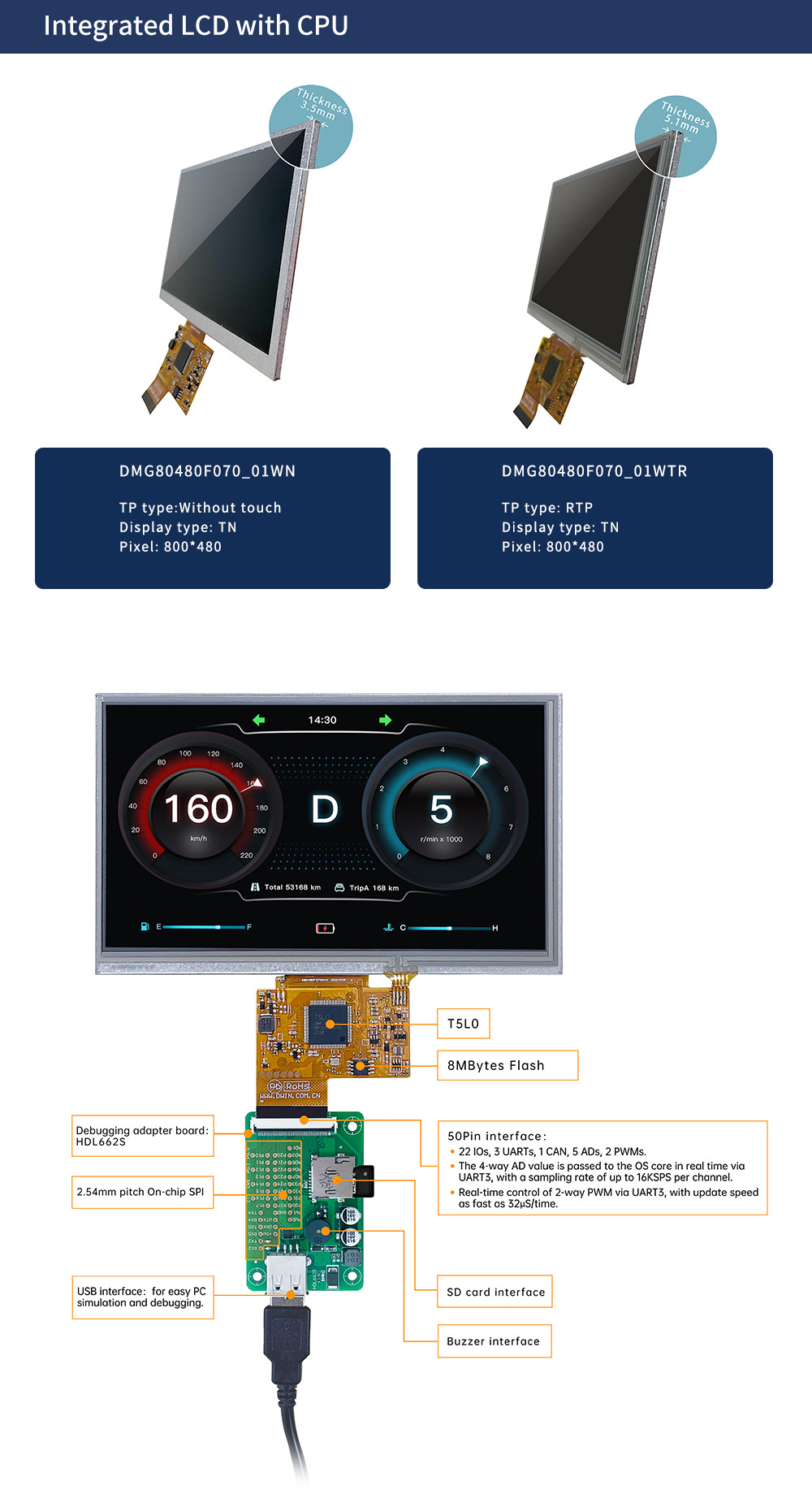

| T5L0 ASIC | ພັດທະນາໂດຍ DWIN.ການຜະລິດຂະຫນາດໃຫຍ່ໃນປີ 2020,1MBytes ຫຼື Flash ໃນຊິບ, ພື້ນທີ່ເກັບຮັກສາຕົວແປ 128Kbytes ສໍາລັບການແລກປ່ຽນຂໍ້ມູນກັບ OS CPU Core ແລະຫນ່ວຍຄວາມຈໍາ.Rewrite cycle: ຫຼາຍກວ່າ 100,000 ເທື່ອ | ||

| ສີ | 262K ສີ | ||

| ປະເພດ LCD | TN, TFT LCD | ||

| ມຸມເບິ່ງ | ມຸມເບິ່ງປົກກະຕິ, ຄ່າປົກກະຕິ 70°/70°/30°/40°(L/R/U/D) | ||

| ພື້ນທີ່ສະແດງ (AA) | 154.08mm (W) × 85.92mm (H) | ||

| ຄວາມລະອຽດ | 800×480 | ||

| ແສງຫຼັງ | LED | ||

| ຄວາມສະຫວ່າງ | DMG80480F070_01WN: 250nit | ||

| DMG80480F070_01WTR: 200nit | |||

| ປະເພດ | RTP (ແຜງສໍາຜັດຕ້ານທານ) | ||

| ໂຄງສ້າງ | ຟິມ ITO + ແກ້ວ ITO | ||

| ແຕະໂໝດ | ສະຫນັບສະຫນູນຈຸດສໍາຜັດແລະລາກ | ||

| ຄວາມແຂງຂອງພື້ນຜິວ | 3H | ||

| ການຖ່າຍທອດແສງ | ຫຼາຍກວ່າ 80% | ||

| ຊີວິດ | Dotting > 1,000,000 ເທື່ອ;Stroke > 100,000 ເທື່ອ;ຜົນບັງຄັບໃຊ້ 150g, ກັບຄືນໄປບ່ອນ ແລະນັບເປັນສອງຄັ້ງ | ||

| ແຮງດັນໄຟຟ້າ | 3.6~5.5V | ||

| ປະຈຸບັນການດໍາເນີນງານ | VCC = +5V, Backlight ເປີດ, 410mA | ||

| VCC = +5V, Backlight off, 115mA | |||

| ອຸນຫະພູມເຮັດວຽກ | -10 ℃ ~ 60 ℃ | ||

| ອຸນຫະພູມການເກັບຮັກສາ | -20 ℃ ~ 70 ℃ | ||

| ຄວາມຊຸ່ມຊື່ນທີ່ເຮັດວຽກ | 10%~90%RH, ຄ່າປົກກະຕິຂອງ 60% RH | ||

| Baudrate | 3150~3225600bps | ||

| ແຮງດັນຂາອອກ | ຜົນຜະລິດ 1, Iout = 8mA;3.0~3.3V | ||

| ຜົນຜະລິດ 0, Iout =-8mA;0~0.3V | |||

| ແຮງດັນຂາເຂົ້າ(RXD) | ວັດສະດຸປ້ອນ 1;3.3V | ||

| ວັດສະດຸປ້ອນ 0;0~0.5V | |||

| ການໂຕ້ຕອບ | UART2: TTL; | ||

| UART4: TTL; (ສາມາດໃຊ້ໄດ້ຫຼັງຈາກການຕັ້ງຄ່າ OS ເທົ່ານັ້ນ) | |||

| UART5: TTL; (ສາມາດໃຊ້ໄດ້ຫຼັງຈາກການຕັ້ງຄ່າ OS ເທົ່ານັ້ນ | |||

| ຮູບແບບຂໍ້ມູນ | UART2: N81; | ||

| UART4: N81/E81/O81/N82;4 ໂຫມດ (ການຕັ້ງຄ່າ OS) | |||

| UART5: N81/E81/O81/N82;4 ໂຫມດ (ການຕັ້ງຄ່າ OS) | |||

| ເຕົ້າຮັບ | 50Pin_0.5mm FPC | ||

| Flash | 8M Bytes | ||

| PIN | ຄໍານິຍາມ | I/O | ລາຍລະອຽດການທໍາງານ |

| 1 | +5V | I | ການສະຫນອງພະລັງງານ, DC3.6-5.5V |

| 2 | +5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 ການປ້ອນຂໍ້ມູນ ADCs.ຄວາມລະອຽດ 12-bit ໃນກໍລະນີຂອງການສະຫນອງພະລັງງານ 3.3V.ວັດສະດຸປ້ອນ 0-3.3V ແຮງດັນ.ຍົກເວັ້ນ AD6, ຂໍ້ມູນສ່ວນທີ່ເຫຼືອແມ່ນຖືກສົ່ງໄປຫາ OS core ຜ່ານ UART3 ໃນ ເວລາຈິງດ້ວຍອັດຕາການເກັບຕົວຢ່າງ 16KHz.AD1 ແລະ AD5 ສາມາດໃຊ້ໃນ ຂະຫນານ, ແລະ AD3 ແລະ AD7 ສາມາດຖືກນໍາໃຊ້ໃນຂະຫນານ, ເຊິ່ງເທົ່າກັບສອງ ການເກັບຕົວຢ່າງ 32KHz AD.AD1, AD3, AD5, AD7 ສາມາດຖືກນໍາໃຊ້ໃນຂະຫນານ, ເຊິ່ງ ເທົ່າກັບ 64KHz ຕົວຢ່າງ AD;ຂໍ້ມູນລວມທັງຫມົດ 1024 ເວລາແລະ ຈາກນັ້ນແບ່ງດ້ວຍ 64 ເພື່ອໃຫ້ໄດ້ຄ່າ 64Hz 16bit AD ໂດຍການເກັບຕົວຢ່າງ. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | +3.3 | O | ຜົນຜະລິດ 3.3V, ການໂຫຼດສູງສຸດຂອງ 150mA. |

| 12 | SPK | O | MOSFET ພາຍນອກເພື່ອຂັບ buzzer ຫຼືລໍາໂພງ.ຕົວຕ້ານທານ 10K ພາຍນອກ ຄວນດຶງລົງພື້ນເພື່ອຮັບປະກັນວ່າການເປີດໄຟຢູ່ໃນລະດັບຕ່ໍາ. |

| 13 | SD_CD | IO | ການໂຕ້ຕອບ SD/SDHC, SD_CK ເຊື່ອມຕໍ່ຕົວເກັບປະຈຸ 22pF ກັບ GND ຢູ່ໃກ້ໆ ການໂຕ້ຕອບບັດ SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | IO | |

| 16 | SD_D2 | IO | |

| 17 | SD_D1 | IO | |

| 18 | SD_D0 | IO | |

| 19 | PWM0 | O | 2 ຜົນຜະລິດ PWM 16-ບິດ.ຕົວຕ້ານທານ 10K ພາຍນອກຄວນຈະຖືກດຶງລົງໄປ ພື້ນທີ່ເພື່ອຮັບປະກັນວ່າການເປີດໄຟແມ່ນໃນລະດັບຕ່ໍາ.ແກນ OS ສາມາດຄວບຄຸມໄດ້ໃນເວລາຈິງຜ່ານ UART3 |

| 20 | PWM1 | O | |

| 21 | P3.3 | IO | ຖ້າໃຊ້ RX8130 ຫຼື SD2058 I2C RTC ເພື່ອເຊື່ອມຕໍ່ທັງສອງ IOs, SCL ຄວນເຊື່ອມຕໍ່ກັບ P3.2, ແລະ SDA ເຊື່ອມຕໍ່ກັບ P3.3 ໃນຂະຫນານ. ມີ 10K resistor ດຶງເຖິງ 3.3V. |

| 22 | P3.2 | IO | |

| 23 | P3.1/EX1 | IO | ມັນສາມາດຖືກນໍາໃຊ້ເປັນການລົບກວນພາຍນອກ 1 input ໃນເວລາດຽວກັນ, ແລະ ສະຫນັບສະຫນູນທັງສອງລະດັບແຮງດັນຕ່ໍາຫຼືຮູບແບບການຂັດຂວາງແຂບ trailing. |

| 24 | P3.0/EX0 | IO | ມັນສາມາດຖືກນໍາໃຊ້ເປັນການລົບກວນພາຍນອກ 0 input ໃນເວລາດຽວກັນ, ແລະ ສະຫນັບສະຫນູນທັງສອງລະດັບແຮງດັນຕ່ໍາຫຼືຮູບແບບການຂັດຂວາງແຂບ trailing. |

| 25 | P2.7 | IO | ການໂຕ້ຕອບ IO |

| 26 | P2.6 | IO | ການໂຕ້ຕອບ IO |

| 27 | P2.5 | IO | ການໂຕ້ຕອບ IO |

| 28 | P2.4 | IO | ການໂຕ້ຕອບ IO |

| 29 | P2.3 | IO | ການໂຕ້ຕອບ IO |

| 30 | P2.2 | IO | ການໂຕ້ຕອບ IO |

| 31 | P2.1 | IO | ການໂຕ້ຕອບ IO |

| 32 | P2.0 | IO | ການໂຕ້ຕອບ IO |

| 33 | P1.7 | IO | ການໂຕ້ຕອບ IO |

| 34 | P1.6 | IO | ການໂຕ້ຕອບ IO |

| 35 | P1.5 | IO | ການໂຕ້ຕອບ IO |

| 36 | P1.4 | IO | ການໂຕ້ຕອບ IO |

| 37 | P1.3 | IO | ການໂຕ້ຕອບ IO |

| 38 | P1.2 | IO | ການໂຕ້ຕອບ IO |

| 39 | P1.1 | IO | ການໂຕ້ຕອບ IO |

| 40 | P1.0 | IO | ການໂຕ້ຕອບ IO |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | IO | ການໂຕ້ຕອບ IO |

| 46 | P0.1 | IO | ການໂຕ້ຕອບ IO |

| 47 | CAN_TX | O | CAN ການໂຕ້ຕອບ |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (ພອດ serial UART2 ຂອງ OS core) |

| 50 | UART2_RXD | I |